## 1/f and White Noise in RF MOSFET Oscillators under Low-Level Signal Injection

Feiran Lei<sup>a</sup> and Marvin H. White<sup>b</sup>

<sup>a</sup> Department of Electrical and Computer Engineering, The Ohio State University, USA, <u>lei.39@osu.edu</u>, <sup>b</sup> Department of Electrical and Computer Engineering, The Ohio State University, USA.

## Introduction:

Noise generated in electronic devices affects greatly the performance of communication systems. In oscillators, baseband device noise is up-converted to the RF as phase noise – short-term random frequency fluctuations in the output signal. In receivers, phase noise limits the signal-to-noise ratio (SNR), bit-error-rate (BER), introduces reciprocal mixing with strong interferers and, in a transmitter, corrupts nearby receivers. We use an external low-level injection signal to synchronize an oscillator [Synchronous Oscillator (SO)], which tracks the reference signal and reduces the phase noise of the system [2-3]. We develop a relationship between device baseband noise and an oscillators' RF phase noise and introduce a noise shaping function to describe signal injection into a differential delay-line SO with active inductor-like loads to achieve suppression of the SO phase noise.

## **Delay Line Phase Noise Modeling**

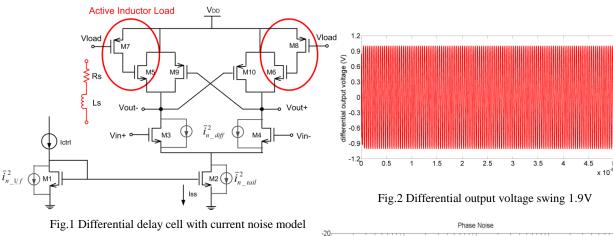

Fig. 1 shows a single delay cell with MOS differential pair M3 and M4, a MOS tail current source M2 (Iss), and active inductor loads M5 M7 and M6 M8. Active inductor loads minimize parasitic capacitance at the output node for high speed operation. PMOS pull up latches M9 and M10 allow the oscillator to achieve a nearly rail to rail swing as shown in Fig. 2 for  $V_{DD} = 1.2V$ . The actual voltage swing Vos has a voltage loss due to the voltage drop across the tail current Iss.

(a) 1/f Noise: 1/f noise fluctuates at a rate much lower than the oscillating frequency. The dominant source of 1/f noise in the differential delay cell resides in M1, which drives the tail current and is amplified in the delay stage. Since fluctuations in each tail current are uncorrelated, the delay variations will accumulate and create significant phase noise. The 1/f noise is modeled as a current source  $\bar{\iota}_{n,1/f}^2$  shown in Fig.1. The expression for the power spectral density (PSD) of the M1 drain current noise is introduced in [1] as

$$S_{I_{n_{-1}/f}}(f) = \eta \cdot \frac{I_{D_1}^2}{f}$$

(1)

where  $\eta = \frac{k_B T}{W_1 L} \left[ \frac{1}{N_n} + (\alpha + \beta) \mu \right]^2 \frac{\rho_t}{\lambda}$  describes noise contribution with fluctuations in free carriers  $N_n^{-1}$  and mobility  $(\alpha + \beta)\mu$ .  $\alpha$  models Coulomb scattering,  $\beta$  surface roughness,  $\lambda$  'tunneling' attenuation, while  $\rho_t$  is the gate stack volume trap density. The PSD, dominated by M1, is

$$S_{I_{SS}}(f) = \eta \cdot \frac{I_{SS}^2}{f}$$

(2)

For the differential delay-line oscillator, the loads may be described by a RC circuit [6] with propagation delay and free running frequency  $t_d = C_{\text{eff}}V_{os}/I_{SS} = R_{\text{eff}}C_{\text{eff}}$  and  $f_o = 1/2Nt_d$ , respectively, where N is the number of delay stages. The sensitivity of the frequency to tail current is  $s_{I_{SS}} = \frac{\partial f_o}{\partial I_{SS}} = \frac{f_o}{I_{SS}}$ , which gives  $S_c(f) = s_c^2 + S_c$   $(f) = \frac{\eta \cdot f_o^2}{\eta}$  and with a narrowband expression [4] the output phase noise at an

gives

$$S_{f_o}(f) = S_{I_{SS}} \cdot S_{I_{SS}}(f) = \frac{1}{f}$$

and with a harrowband expression [4] the output phase noise at an offset frequency of  $\Delta f_{os}$  is

$\mathcal{L}_{1/f}(\Delta f_{os}) = \frac{S_{f_o}(\Delta f_{os})}{4\Delta f_{cs}^2} = \frac{\eta \cdot f_o^2}{4\Delta f_{os}^2}$

(3)

(b)**Thermal Noise:** The period jitter  $\sigma_{T_white}^2$  due to white noise can be found as 2N multiplying the ratio between the output noise voltage and the slope of the differential switching voltage at zero-crossing [5]. For a simplified case, assume only three white noise sources dominating the total phase noise: 1) white noise due to the effective load resistor  $R_{eff}$ ; 2) tail current noise  $\bar{\iota}_{n_tail}^2$  from the tail NMOS M2 during transition time; and 3) current noise  $\bar{\iota}_{n_diff}^2$  from the differential pair M3 and M4 during transition time. Thus, the period jitter can be calculated by the formula:

$$\sigma_{T\_white}^{2} = 2N\sigma_{td}^{2} = 2N\frac{\bar{v}_{n}^{2}}{(I_{SS}/C_{eff})^{2}} = 2N\frac{c_{eff}^{2}}{I_{SS}^{2}} \left[\frac{2k_{B}T}{C_{eff}} + \frac{2k_{B}T\gamma g_{m2}R_{eff}}{\pi C_{eff}} + \frac{3k_{B}T\gamma g_{m3,4}R_{eff}}{2C_{eff}}\right]$$

(4)

The relationship between the period jitter and the phase period can be expressed on [5]:

The relationship between the period jitter and the phase noise can be expressed as [5]:

$\mathcal{L}_{\text{white}}(\Delta f_{oS}) = \sigma_{T_{-}\text{white}}^{2} \frac{f_{o}^{3}}{\Delta f_{oS}^{2}} = \frac{1}{(2NR_{\text{eff}}C_{\text{eff}}I_{SS})^{2}} \left[ \frac{2k_{B}T}{R_{\text{eff}}} + \frac{2k_{B}T\gamma g_{m2}}{\pi} + \frac{3k_{B}T\gamma g_{m3,4}}{2} \right] \cdot \frac{1}{\Delta f_{oS}^{2}}$ (5)

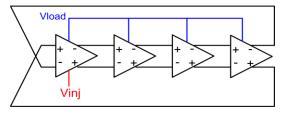

**Injection Locked SO:** The phase noise of the SO in Fig. 3 is reduced substantially by an injection of a low-noise reference to the oscillator, which intuitively can correct the zero-crossing of the output waveform in each period in the time domain, thereby, reducing the jitter accumulation at the output. The noise shaping function with injection is

$$\mathcal{L}_{\Delta}(\Delta f_{os}) = 10\log \frac{\Delta f_{os}^2}{(K_{so}^2 - \Delta f^2) + \Delta f_{os}^2} \tag{6}$$

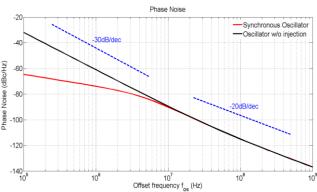

where  $K_{SO}$  is an injection parameter which is also half the SO tracking bandwidth [3].  $\Delta f$  is the frequency difference between injection frequency and oscillator free running frequency (f<sub>o</sub> =3.45GHz). Fig.4 shows the phase noise in the free running oscillator as well as in the SO system. Device baseband 1/f noise is up-converted to high frequency regime with a slope of 1/f<sup>3</sup> (-30dB/dec) while device baseband white noise is up-converted to high frequency regime with a slope of 1/f<sup>2</sup> (-20dB/dec). The SO system reduces the phase noise in the low frequency offset region within the SO tracking bandwidth (30 dB suppression at  $\Delta f_{os} = 100$  KHz).

Fig.3 Synchronous Oscillator (SO) with Injection to reduce the oscillator phase noise

Fig.4 Phase Noise at RF (f<sub>0</sub>=3.45GHz) and up-converted 1/f and white noise. Phase Noise ( $\Delta f_{os}$ =100 KHz) suppressed by 30 dB

## References

[1] X. Zhang and M. H. White, "A quantum mechanical treatment of low frequency noise in high-K NMOS transistors with ultra-thin gate dielectrics," *Solid-State Electronics*, <u>78</u>, 131 (2012)

[2] V. Uzunoglu and M. H. White, "The synchronous oscillator: a synchronization and tracking network," *IEEE J. Solid-State Circuits*, <u>SC-20</u>, 1214 (1985)

[3] F. Lei and M. H. White, "A Preliminary study of the Coherent Phase Synchronous Oscillator (CPSO) for Phase-Locked Loop (PLL) Applications," *MWSCAS'13*, Columbus, OH (2013)

[4] E. Hegazi and A. Abidi, "Varactor characteristics, oscillator tuning curves, and AM-FM conversion," *IEEE J. Solid-State Circuits*, <u>38</u>, 1033 (2003)

[5] A. Abidi, "Phase noise and jitter in CMOS ring oscillators," *IEEE J. Solid-State Circuits*, <u>41</u>, 1803 (2006)

[6] S. Min, et al, "A 90-nm CMOS 5GHz Ring Oscillator PLL with Delay Discriminator-Based Active Noise Cancellation", IEEE J. Solid State Circuits, **SC-48**, 1151 (2013)