## Electron mobility improvement due to GaO<sub>x</sub> passivation layer formed by pre-deposition annealing in HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As nMISFET with sub-1.0 nm EOT

<u>Minoru Oda</u><sup>a</sup>, Toshifumi Irisawa<sup>a</sup>, Wipakorn Jevasuwan<sup>a</sup>, Tatsuro Maeda<sup>a</sup>, Yuuichi Kamimuta<sup>a</sup>, Osamu Ichikawa<sup>b</sup>, Toshio Ishihara<sup>b</sup>, Takenori Osada<sup>b</sup>, and Tsutomu Tezuka<sup>a</sup>

<sup>a</sup> Green Nano-electronics center,AIST,Japan,minoru2.oda@aist.go.jp, <sup>b</sup> Tsukuba Material Development Laboratory, Sumitomo Chemical Co., Ltd., Japan,

The electron mobility of  $HfO_2/InGaAs$  nMSIFETs has been found to be significantly enhanced by predeposition annealing before atomic layer deposition (ALD) of  $HfO_2$  and the record high electron mobility in sub-1.0 nm EOT regime has been demonstrated. XPS measurements revealed that the pre-deposition annealing increased  $GaO_x$  and reduced  $AsO_x$  at the MIS interface, which was considered to result in the reduction of  $D_{it}$ as well as charge traps.

InGaAs nMISFETs are attracting much attention for the alternative to Si nMISFETs because of their high electron mobility. Although HfO<sub>2</sub> (k ~ 20) is suitable for EOT scaling [1, 2], it has been reported that the mobility of InGaAs surface channel MISFETs with HfO<sub>2</sub> gate dielectric is much lower than that with Al<sub>2</sub>O<sub>3</sub> (k ~ 9). The lower mobility is due to interface states and/or roughness [3-5]. In this study, we propose a simple way, pre-deposition annealing before HfO<sub>2</sub> deposition, to effectively improve HfO<sub>2</sub>/InGaAs MIS interface quality and increase the mobility.

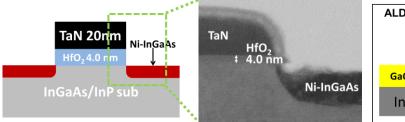

Fig. 1 shows a schematic of  $HfO_2/In_{0.53}Ga_{0.47}As$  nMISFET and its cross sectional TEM image. The device was fabricated as follows. An  $In_{0.53}Ga_{0.47}As$  substrate with  $N_a = 3x10^{16}$  cm<sup>-3</sup> was pretreated with  $(NH_4)_2S$  for 2 min and successively loaded into an ALD chamber. The substrate was annealed at 300 °C for 30 min in Ar atmosphere (5 torr) just after loading. Then it was cooled down to 200 °C and 50-cycle HfO<sub>2</sub> (~4.0 nm) was deposited. In a reference sample, 50-cycle HfO<sub>2</sub> was deposited at 200 °C just after loading.

A gate metal, TaN 20 nm, was deposited after  $HfO_2$  deposition. Gate was defined by RIE and self-aligned Ni-InGaAs alloyed S/D contacts were formed by N<sub>2</sub> annealing at 350 °C for 5 min. Al SD contact and back contact was formed for a reduction of contact resistance.

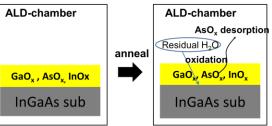

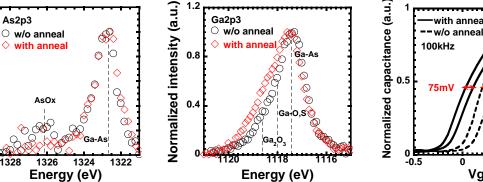

Surface chemical states of HfO<sub>2</sub>/InGaAs investigated by XPS measurements are shown in Fig. 2(a). It is clearly seen that an intensity of GaO<sub>x</sub> peak is increased by the pre-disposition annealing, indicating the formation of interfacial GaO<sub>x</sub> layers during annealing. The thickness of GaO<sub>x</sub> estimated by XPS [6, 7] was <0.23 nm with the annealing. On the other hand, an AsO<sub>x</sub> peak shows slight reduction with the annealing. These phenomena could result from the oxidation of Ga atoms by residual oxidant (H<sub>2</sub>O) and the thermal desorption of unstable AsO<sub>x</sub> (Fig. 2(b)).

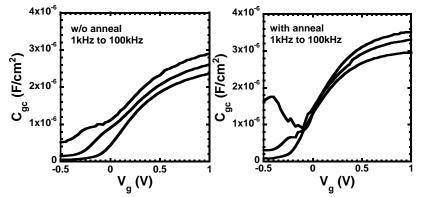

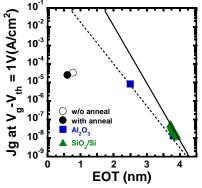

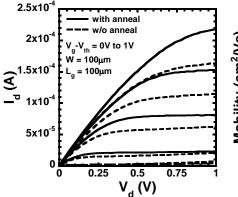

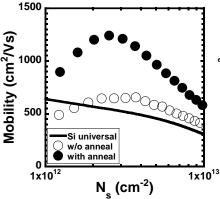

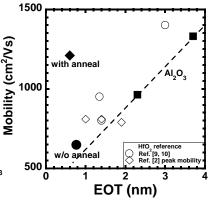

Fig. 3 shows gate to channel capacitance, Cgc, characteristics measured from 1 kHz to 100 kHz. It is seen that the annealed sample has much smaller frequency dispersion around flat band voltage, suggesting the reduction of  $D_{it}$  in band gap [5, 8]. Besides, the annealed sample has much smaller hysteresis than that in the un-annealed sample (Fig. 4), indicating that the pre-deposition annealing decreases not only  $D_{it}$  but also the charge trap density. These results are attributable to the effective passivation by the thin interfacial GaO<sub>x</sub> layer, as suggested by Jevasuwan et al. [7]. No Cgc reduction due to the pre-deposition annealing suggests no EOT penalty caused by the thin interfacial GaOx layer formed here. In fact, the EOT of pre-deposition annealed one was estimated to be 0.6 nm by fitting its Cgc-100kHz. Gate leakage was also confirmed to be almost unchanged by the pre-deposition annealing and it is four orders of magnitude smaller than that of Al<sub>2</sub>O<sub>3</sub>/InGaAs in sub-1.0 nm regime (Fig. 5). Fig. 6 shows I<sub>d</sub>-V<sub>d</sub> characteristics of both devices with and without the pre-deposition annealing. Substantial increase of  $I_d$  by pre-deposition annealing is observed. Inversion-layer electron mobility against surface carrier density,  $N_s$ , is shown in Fig. 8. The mobility is confirmed to be significantly enhanced by the pre-deposition annealing (Fig. 7), which is thanks to the improved MIS interface quality as seen in Figs 3 and 4. Fig. 8 summarizes EOT-mobility trend of In<sub>0.53</sub>Ga<sub>0.47</sub>As nMISFETs with Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> gate dielectrics, including the values reported by the other groups. Our device with HfO<sub>2</sub> shows the highest mobility in the sub-1 nm EOT regime. It is, therefore, concluded that HfO2/InGaAs nMIFETs with pre-deposition annealing is promising to realize high mobility InGaAs nMISFETs with extremely thin EOT.

## Acknowledgements

This research is granted by JSPS through FIRST Program initiated by CSTP. **References**

[1] Y. Xuan et al., IEDM, 637, 2007 [2] H. Zhao et al., J. vac. Sci. Tehnol. B, 27(4), 2024, 2009 [3] N. Taoka et al., IEDM, 610, 2011 [4] A. M. Sonnet et al., Microelectron. Eng., 88, 1083, 2011 [5] M. Oda et al., SSDM, 797, 2012 [6] C. L. Hinkle et al., Micorelectron. Eng., 86, 1544, 2009 [7] W. Jevasuwan et al., SISC, 7.4, 2012 [8] H. Zhao et al., Appl. Phys. Lett., 95, 253501, 2009 [9] Y.-T. Cheng et al., IEEE Trans. Electron Device Lett., 32, 1531, 2011 [10] J. Lin et al., IEDM, 401, 2008

Fig. 1 A schematic of HfO2/InGaAs nMISFET and its cross sectional TEM image.

Normalized intensity (a.u.)

1.2

1

0.8

0.6

0.4

0.2 0 As2p3

Fig. 2(b) A model of the  $GaO_x$  formation and  $AsO_x$ desorption in an ALD chamber.

with anneal

Fig. 2(a) As2p3 (left) and Ga2p3 (right) peak measured by XPS for HfO<sub>2</sub> 10cycle/InGaAs with and without pre-deposition annealing.

0.5 0 Vg (V) Fig. 4 Hysteresis of Cgc for each device measured at 100 kHz.

Fig. 3 Cgc-Vg plot of HfO2/InGaAs nMSIFET with and without predeposition annealing.

Fig. 6 I<sub>d</sub>-V<sub>d</sub> characteristics of devices with and without pre-deposition annealing.

Fig. 7 Electron mobility against surface carrier density, N<sub>s</sub>, of devices with and without pre-deposition annealing.

Fig. 5  $J_g$  at  $V_g$ - $V_{th} = 1V$  in HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/InGaAs and SiO<sub>2</sub>/Si nMOSFET.

Fig. 8 Mobility v.s EOT for various gate-stack at  $N_s = 3x10^{12}$  cm<sup>-2</sup>. Black solid dots represent data of this work.