## A Generic Analytical Current Model for Hetero-Junction Double-Gate Tunnel-FETs Including Two-Dimensional Effects

Michael Graef a,b, Thomas Holtij a,b, Franziska Hain a,b, Alexander Kloes a, and Benjamín Iñíguez b

## <sup>a</sup> Competence Center for Nanotechnology and Photonics, Technische Hochschule Mittelhessen, Giessen, Germany, michael.graef@ei.thm.de, <sup>b</sup> DEEEA, Universitat Rovira i Virgili, Tarragona, Spain.

In the last few years the downscaling of MOSFETs has caused problems due to the increasing short-channel effects (SCEs) in the sub 22 nm technology. The conventional MOS transistor has its physical limits due to the drift-diffusion current transport mechanism resulting in a minimal subthreshold-slope of  $60 \frac{mv}{dec}$ . To fall below this physical limit a new device technology with an alternative carrier transport mechanism is needed to allow for reduced operating voltage and lower energy consumption. The Tunnel-Field-Effect-Transistor (TFET) is a promising device because of its band-to-band tunneling carrier transport mechanism at the channel junctions [1]. Carriers entering the channel region are limited by "band pass filtering" with respect to their energy. Recently fabricated devices show a slope S of  $40 \frac{mv}{dec}$  [2]. In order to simulate complex circuits and predict the electrical behavior special to TFETs a physics-based, analytical model is needed. The introduced model presents a new generic approach to investigate state of the art hetero junctions in Tunnel-FETs for performance enhancement.

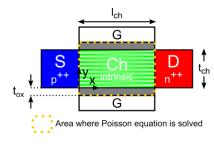

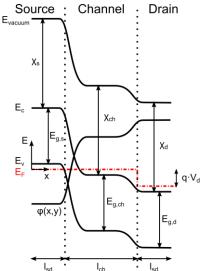

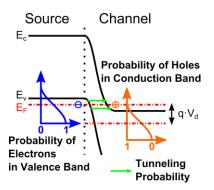

Figure 1 shows the geometry of a double-gate n-Tunnel-FET. The source area is highly p-doped and the drain area highly n-doped. The channel area remains intrinsic. In order to analyze the performance of hetero-junction TFETs the channel material is set to the most commonly fabricated device materials: Si, Si<sub>0.5</sub>Ge<sub>0.5</sub>, GaAs, and In<sub>0.53</sub>Ga<sub>0.47</sub>As. The electrostatics of the device are two-dimensionally modeled only in the channel region neglecting mobile channel charges. A model for an effective built-in potential at the channel junctions and a 1D parabolic potential solution in the source and drain area was implemented to improve the solution [3]. Applying the improved boundary conditions the electrostatics of the device are calculated by solving the Poisson equation two-dimensionally with the conformal mapping technique including the Schwarz-Christoffel transformation as described in [4], [5], [6]. With the given potential solution the band structure of the device is estimated including band gap narrowing in the doped areas. To correctly model the hetero junctions the material dependent parameters like electron affinity  $\gamma$ and band gap  $E_g$  are taken into account. Figure 2 shows the potential solution  $\varphi(x,y)$  and the estimated band structure with all parameters needed. With the given band structure of the device the tunneling probability is calculated quasi two-dimensionally using the Wentzel-Kramers-Brillouin (WKB) approximation [7]. Therefore, we divide the channel area in horizontal slices (see Fig. 1). After calculating the tunnelling distances  $x_n$  using the 1D parabolic potential solution in the source area (yellow line) and an additional parabolic function for the approximation of the potential in the first few nm of the channel region (orange line), the tunneling probability is calculated at every point in the channel region where tunneling can happen for every channel slice (Fig. 3). With the Fermi distributions in the different areas the band-to-band tunneling current can be calculated assuming a constant Fermi level directly at the junctions (Fig. 4). The band-to-band tunneling current is calculated for every tunneling path at the channel junctions using the Landauer transmission theory [8]. By integrating these results the overall device current is determined. Trap assisted tunneling was neglected in the model and in the simulation.

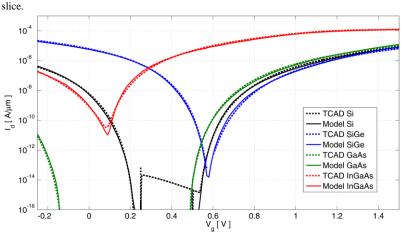

The model results are compared against the finite-element-method (FEM) simulator TCAD Sentaurus. In the simulation a non-local band-to-band tunneling model was applied. Figure 5 shows the current transfer characteristics of the device for the different channel materials with fitted values for the effective carrier masses, tunneling mobilities, minimal tunneling barrier heights and screening lengths for the effective built-in potential calculation. The model matches well with the simulation data. In summary, one can say that the selection of the channel material has mayor influence of the device performance. By using semiconductors with a smaller bandgap, better effective carrier masses and mobilities the minimal OFF-state current increases and therefore the subthreshold slope worsens. But relative to the threshold voltage shift the maximum ON-state current improves for decreasing bandgaps.

Fig. 1: Geometry of a DG n-TFET showing its doping profile, structural parameters and channel slices for current calculation. Within the dotted yellow line the Poisson equation is solved.

Fig. 2: Evaluation of the band structure with material dependent parameters and the 2D potential solution  $\varphi(x,y)$  along a channel slice

Fig. 3: Schematic band structure for a DG n-Tunnel-FET with 2D approach for the tunnelling probability showing the parabolic band structure approaches for the tunneling distance calculation (yellow and orange part of  $E_v$ ). The triangles are used for the WKB approximation.

Fig. 4: Schematic band structure of a DG n-Tunnel-FET at the source-to-channel junction showing the Fermi distributions in the ONstate.

Figure 5: Model results of the current transfer characteristics of a DG n-Tunnel-FET for different channel materials compared against TCAD Simulation data at  $V_d = 0.7$  V.

## References

W. Choi, B. Park, J. Lee, and T. Liu, "Tunneling field-effect transistors (tfets) with subthreshold swing (ss) less than 60 mv/dec," Electron Device Letters, IEEE, vol. 28, no. 8, pp. 743–745, 2007.

A. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond cmos logic," Proceedings of the IEEE, vol. 98, no. 12, pp. 2095 –2110, dec. 2010.

[3] T. Dutta, Q. Rafhay, G. Pananakakis, and G. Ghibaudo, "Modeling of the Impact of Source/Drain regions on Short Channel Effects in MOSFETs."

[4] M. Schwarz, T. Holtij, A. Kloes, and B. Iñíguez, "2D Analytical Framework for Compact Modeling of the Electrostatics in Undoped DG MOSFETs," in Proceedings of MIXDES, Gliwice, Poland, 2011.

[5] M. Schwarz, T. Holtij, A. Kloes, and B. Iñíguez, "2D analytical calculation of the electric field in lightly doped Schottky barrier doublegate MOSFETs and estimation of the tunneling/thermionic current," Solid-State Electronics, vol. 63, no. 1, pp. 119 – 129, 2011.

[6] M. Graef, T. Holtij, F. Hain, A. Kloes, and B. Iñíguez, "Two-dimensional Physics-based Modeling of Electrostatics and Band-to-Band Tunneling in Tunnel-FETs," in Proceedings of MIXDES, Gdynia, Poland, 2013.

[7] A. Gehring, "Simulation of tunneling in semiconductor devices," Ph.D. dissertation, TU Wien, 2003.

[8] E. Gnani, S. Reggiani, A. Gnudi, and G. Baccarani, "Drain-conductance optimization in nanowire TFETs." in Solid-State Device Research Conference (ESSDERC), 2012 Proceedings of the European, pp. 105–108, IEEE, 2012.